文章

212

粉丝

0

获赞

0

访问

28.7k

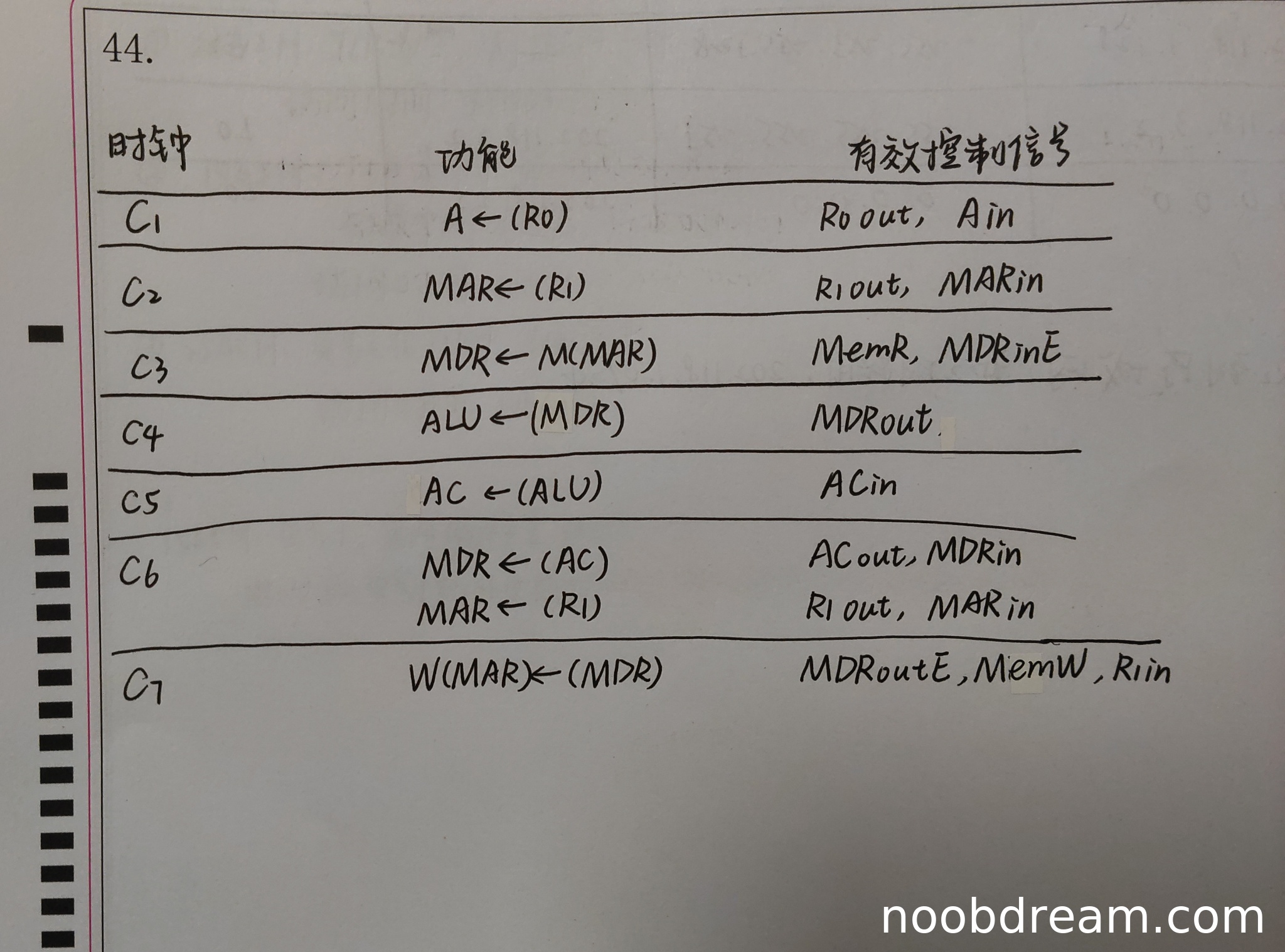

2009年计算机学科专业基础综合试题 - 第44题回答

评分及理由

(1)得分及理由(满分13分)

学生答案存在多处逻辑错误:

- C1阶段过早将R0存入A,此时还未读取内存数据,不符合指令执行顺序。

- C4阶段仅将MDR输出到ALU但未执行加法操作,缺少Add控制信号。

- C5阶段将ALU结果存入AC,但ALU未接收来自A的输入,加法操作不完整。

- C6阶段重复执行MAR←(R1),这是不必要的操作,且同时执行MDR←(AC)会浪费时钟周期。

- C7阶段包含R1in控制信号,但指令不需要写入R1寄存器。

- 整体执行流程比标准答案多出1-2个时钟周期,效率较低。

虽然学生理解了基本的数据通路操作,但执行顺序和控制信号存在明显逻辑错误。根据参考答案,正确的执行需要5-6个时钟周期,而学生方案用了7个周期且有多处冗余和错误。

得分:5分(主要考虑到学生理解了部分数据通路操作,但执行逻辑有严重问题)

题目总分:5分

The road of your choice, you have to go on !

粤ICP备16082171号-1

The road of your choice, you have to go on !

粤ICP备16082171号-1

登录后发布评论

暂无评论,来抢沙发